首页 > 文秘写作 > 毕业设计 / 正文

基于FI,FO的色选机分选系统设计

2023-03-11 09:40:14 ℃于瑞红 张雨丰 李立新 李 玲 王佳慧

(防灾科技学院电子科学与控制工程学院,河北 廊坊 065201)

色选机分选系统主要功能是对检测系统输出的检测信号进行采集和处理,并为分选电磁阀输出有一定延时和宽度的分选脉冲信号[1]。多通道色选机中每个通道信号是完全无关且完全随机的,通常采用各个通道完全独立分开的处理方法,这就需要对各个通道的每个信号进行处理和延时[2-3]。当用DSP(Digital Signal Processor)、ARM(Advanced Risc Machines)等处理器实现分选系统中的信号处理和延时控制时,由于处理器程序顺序执行的特点,在通道数比较多时,信号处理的实时性和一致性较差,延时时间和分选脉冲时间精度差,影响色选机的分选效果[4-5]。

综上,考虑到色选机分选系统通道数多、信号控制精度高、实时性高等控制要求,以高速并行FPGA为控制核心,设计了分选系统的通信、控制、驱动等硬件电路,提出了信号精确无损的控制策略[6-7],给出了分选系统各个子程序模块的实现方式,并利用仿真和实验平台验证了分选系统的性能。

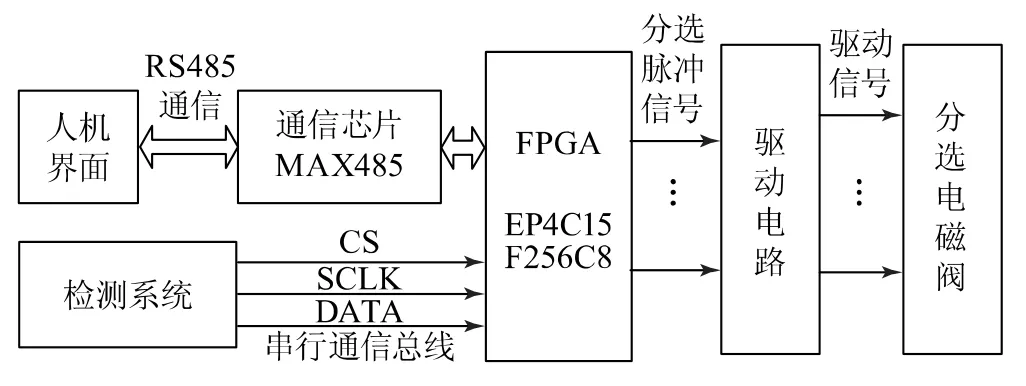

分选系统结构框图如图1所示。人机界面通过RS485总线与分选系统进行数据交换,以实现分选参数的实时调整和通信;

检测系统通过串行通信总线给分选系统传输检测信号;

选用FPGA为分选系统的控制核心,完成检测信号的串并转换和精确无损延时,分选脉冲信号的产生,通用异步收发器(Universal Asynchronous Receiver Transmitter,UART)接口模块实现及通信等功能。

图1 分选系统框图

分选系统的硬件主要由通信电路、信号产生电路和驱动电路三部分组成。

分选系统通过RS485总线和人机界面进行数据交换,接收人机界面设定的延时时间、动作时间等参数,并向人机界面发送状态、故障等信息。

信号产生电路采用以EP4C15F256C8为核心的FPGA芯片实现检测信号延时、分选脉冲信号产生等功能。该芯片具有504K的内部RAM、15 000多个LE、4个PLL锁相环和165个I/O口,其中具有差分输入功能的有53个,可以满足本控制系统的性能要求。

驱动电路采用多个半桥驱动芯片DRV8844PWP驱动分选电磁阀,每个驱动芯片可驱动4个电磁阀。

当色选机检测到异常物料时,分选系统需要对分选电磁阀输出一个具有一定延时和宽度的数字脉冲信号作为控制信号。根据待分选物料种类和机械调节位置的不同,从检测系统检测到异色物料和杂质到分选电磁阀动作一般需要几毫秒到十几毫秒的时间,且色选机有几十到几百个通道的物料需要同时处理,因此分选系统需要把检测系统所有通道的信号延时一段时间,再用延时后的信号驱动分选电磁阀打开喷气喷嘴,完成对异色物料和杂质的剔除。如果待分选物料比较小,则其通过分选电磁阀喷嘴的时间就非常短,一般只有0.5~2 ms,导致分选系统对延时时间的控制精度要求非常高,控制精度一旦大于0.1 ms,将直接导致无法选出异色物料或误选出正常物料的情况,从而严重影响检出效果。

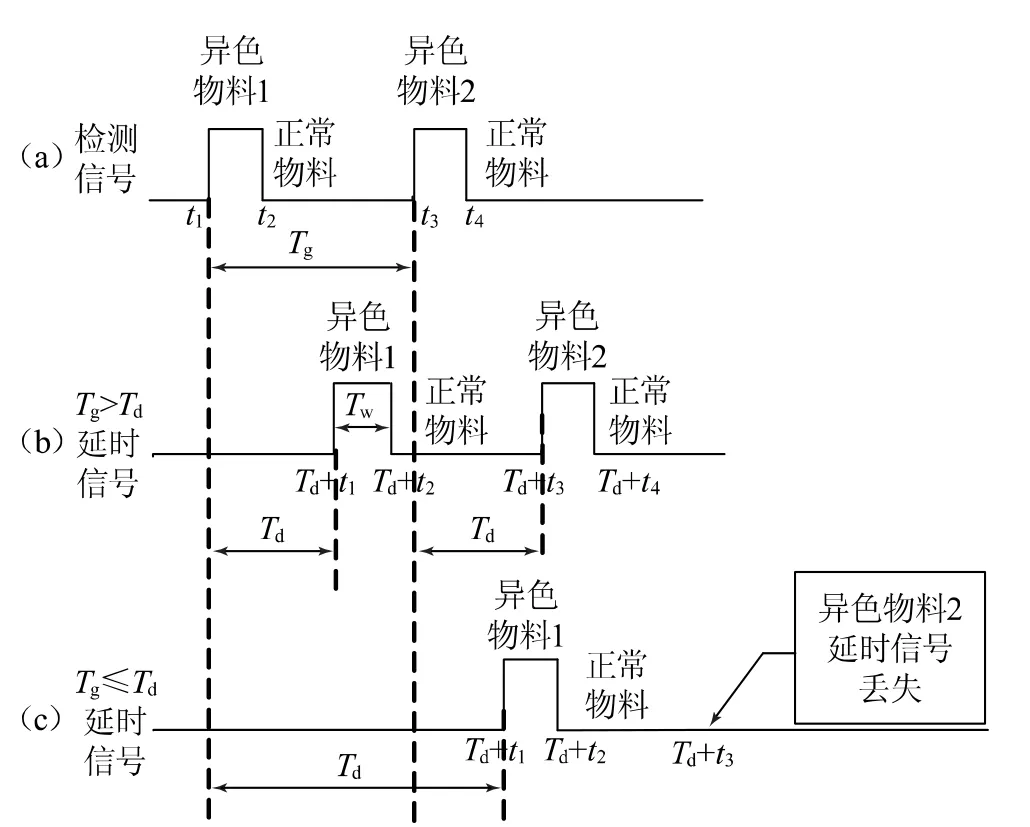

以DSP等处理器为控制核心的分选系统,每个通道的检测信号延时一般通过对每一通道信号的上升沿和下降沿分别进行计数实现。假定每个通道中有两个异色物料信号输入,如图2(a)所示,t1、t3时刻表示两个异色物料信号的开始,也是输出脉冲延时计数的开始,t2、t4时刻是两个异色物料信号的结束。

图中Tg、Td分别表示两个信号之间的时间间隔、输出脉冲的延时时间。当Tg>Td时,延时信号如图2(b)所示,两个异色物料信号延时后的信号不会丢失,这种延时方法,每个通道需要2个计数器,在通道比较少的时候较容易实现,但通道比较多时,计数器就会占用大量的资源,硬件成本奇高。

当Tg≤Td时,第一个异色物料信号开始的时刻为t1,经过计数器计数延时Td时间后输出延时信号,第二个异色物料信号开始时刻为t3,此时需要该通道的计数器开始计数延时,但由于Tg≤Td,在第二个异色物料的信号到达时,计数器还在计数工作中,因此第二个异色物料的延时时间无法正常计数,导致延时信号中第二个异色物料的信号丢失,使第二个异色物料不能有效检出,如图2(c)所示。同理,当Tg≤Td且出现多个异色物料信号时,在Td时间内分选系统只能输出第一个异色物料的延时信号,其余的异色物料信号全部丢失。

图2 检测信号延时图

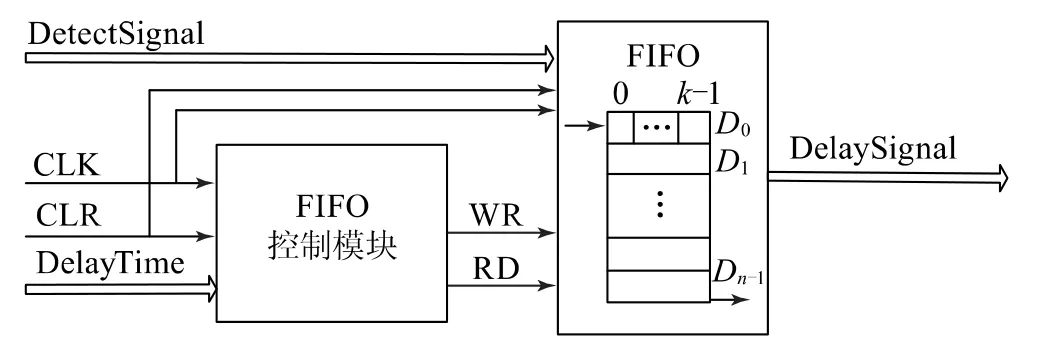

鉴于以上分析,提出利用FIFO数据先入先出特点实现信号延时功能的控制策略,如图3所示。

图3 FIFO控制模块

CLK为时钟信号,FIFO控制模块在每个时钟的上升沿产生FIFO的写使能信号WR和读使能信号RD,写使能信号将数据D0写入FIFO,同时读出FIFO内的数据Dn-1,由于FIFO具有先入先出的特性,经过FIFO的数据延时的时间为:

式中:TCLK为时钟信号CLK的周期;

n为读使能信号RD滞后写使能信号WR的CLK时钟数。

设k为分选系统通道数,每个通道对应一位数据,k个通道的检测信号组成一个k位数据,由此FPGA的内部RAM配置成k位宽度的同步FIFO。通过此种方法,分选系统的多通道信号按照设定延时时间Td进行高精度的延时,延时前后的信号完全一致,避免了以处理器为控制核心的分选系统中连续异常物料信号丢失情况的出现。

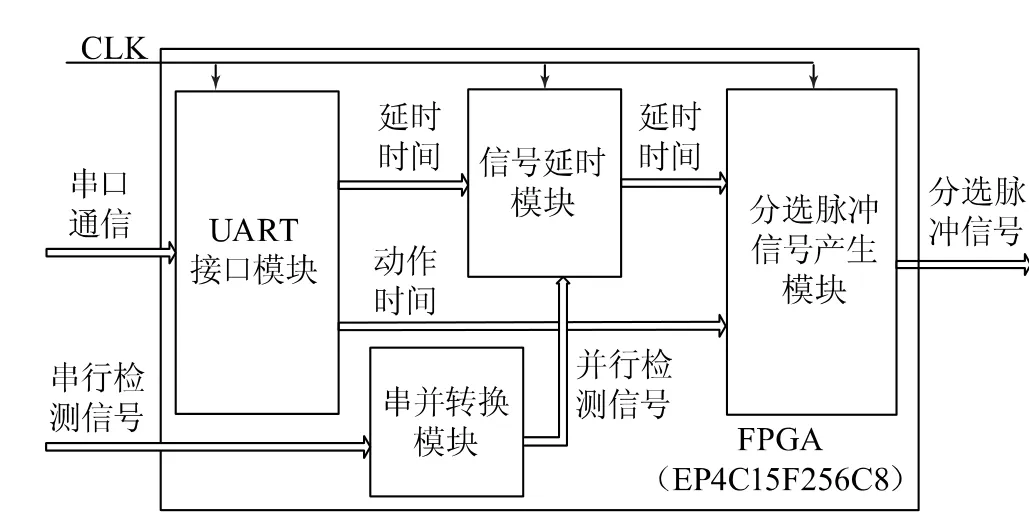

FPGA作为分选系统的控制核心,软件结构框图如图4所示,主要包含4个子程序模块:UART接口模块、串并转换模块、信号延时模块和分选脉冲信号产生模块。

图4 FPGA程序结构框图

4.1 UART接口模块

在FPGA内部实现UART接口模块,以实现UART串行通信功能。UART接口模块由DI(数据输入)、RO(数据输出)、RE(接收使能)、DE(发送使能)4种信号构成。UART接口模块采用VHDL语言编写,包含发送、接收和波特率发生器3个模块,实现FPGA与485驱动芯片的数据交换功能。

4.2 串并转换模块

色选机的检测系统实时检测待分选的物料,并把检测信号传输给分选系统。为了方便布线,检测信号一般采用串行的传输方式,即通过3根信号线CS、SCLK、DATA进行串行传输。CS是使能信号,传输数据时有效;

SCLK是时钟信号,用于同步传输数据,每个时钟信号传输一位数据;

DATA是传输的数据信号。接收的串行数据信号DATA通过FPGA的串并转换程序模块,在CS信号有效时,在SCLK的每个上升沿进行采集,经过k个SCLK信号上升沿,完成k位检测信号的串并转换[8]。

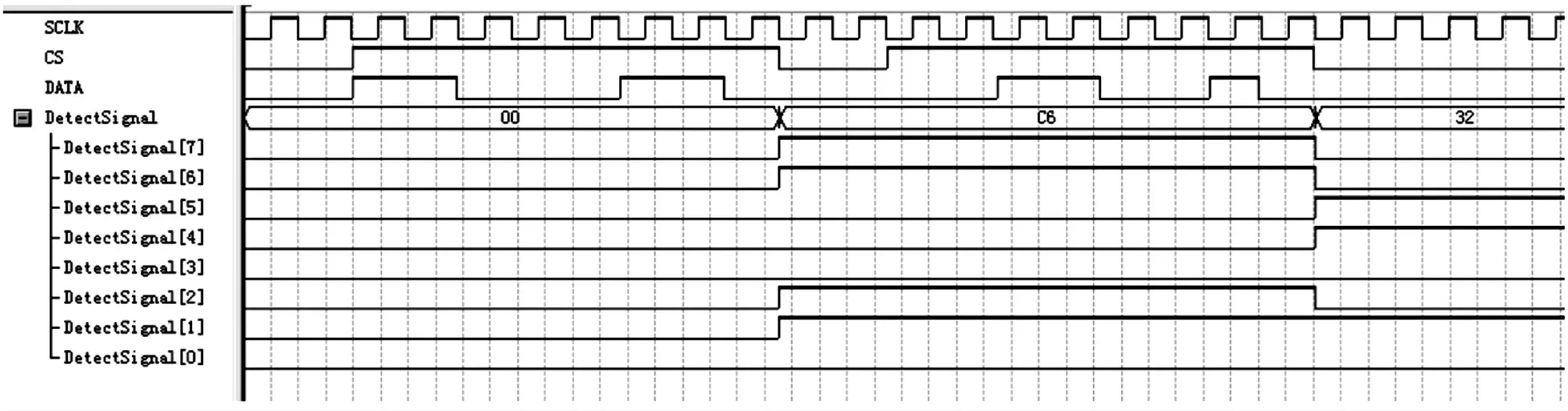

以8通道的分选系统为例建立仿真模型,仿真结果如图5所示。每个通道对应一位数据,因此检测系统传输给分选系统的检测信号是一个8位的数据,通过使能信号CS和同步时钟信号SCLK把串行数据DATA转换成8位并行数据DetectSignal。

图5 8通道分选系统串并转换仿真图

4.3 信号延时模块

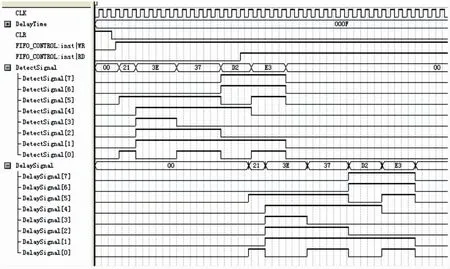

根据信号延时控制策略,由FPGA芯片的内部FIFO及其控制模块实现多路信号延时功能。以k=8的分选系统为例,延时信号的产生仿真图如图6所示。CLK为TCLK=0.1 ms的时钟信号,读使能信号滞后写使能信号时钟数n=DelayTime,DetectSignal为检测信号,DelaySignal为经过延时后的延时信号。从仿真图中可以看出,设定延时时间1.5 ms,由公式(1)可得DelayTime=15,延时后的信号0x21、0x3E、0x37、0xD2、0xE3与延时前的检测信号完全一致,延时精度为CLK的周期0.1 ms,完全满足分选系统的要求。

图6 延时信号产生仿真图

4.4 分选脉冲信号产生模块

分选脉冲信号产生模块将根据各个通道的延时信号和设定的动作时间输出各分选电磁阀的分选脉冲信号。根据待分选物料的大小及其通过分选电磁阀喷嘴速度的不同,分选电磁阀的动作时间Tw也不同,动作时间由人机界面设定。在FPGA内部为每一通道的电磁阀动作时间做一个单稳态计数器,在延时信号的上升沿开始计数,并输出分选信号,计数到达设定动作时间后停止计数,并关闭分选信号。利用FPGA程序并行执行的特点,各通道的计数器单独工作,计数准确,可以满足各通道分选电磁阀控制的要求。

5.1 实验平台构建

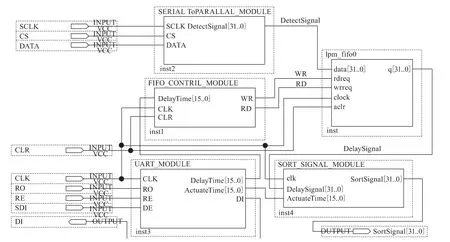

构建通道数k=32的色选机作为实验平台,实验色选机分选系统FPGA程序如图7所示。SERIALToPARALLAL_MODULE为串行检测数据转换为并行检测数据的串并转换模块;

lpm_fifo0为配置成宽32、最大深度2 048的同步FIFO;

UART_MODULE为485通信的接口模块,实现参数数据的设定;

SORT_SIGNAL_MODULE为分选脉冲信号产生模块。

图7 分选系统的FPGA程序

实验过程中,选择实验物料密度为1.6 g/cm3,根据机械及物料特性设定延时时间DelayTime为10.5 ms,设定动作时间ActuateTime为1.8 ms。

5.2 结果与分析

实验物料中坏物料的比例约为5.5%,在不同产量的实验结果如表1所示。

表1 实验物料分选试验结果

实验结果表明,随着色选机产量的逐渐增加,坏物料的检出比逐渐下降,好物料的带出比逐渐增加,当产量为600 kg/h时,坏物料的检出比为98.5%,好物料的带出比为3.3%,满足用户实际需求,较传统的32通道色选机分选系统(产量只能达到300 kg/h)已有非常大的提高。

本项目开发设计了一个实时性高、分选速度快、控制精度高的大米色选机分选系统。该系统将FPGA内部RAM配置成FIFO,FIFO的位宽与分选系统通道数相同,读使能信号滞后写使能信号时钟数与检测信号的延时时间成正比,通过控制FIFO读写实现分选系统多通道信号的精确无损延时。同时利用FPGA程序并行执行的特点实现检测信号的串并转换,并行产生分选电磁阀的分选脉冲信号等功能,并通过485总线实时传输延时参数和动作时间参数。该系统克服了早期分选系统连续异色米粒和杂质信号丢失及多通道信号占用资源多、硬件成本高、分选脉冲信号一致性差的缺点。应用结果表明,该设计突破了色选机在多通道、高产量、高精度分选系统中的技术瓶颈,对提高色选机的检出水平和产量具有重要意义。

猜你喜欢 异色选机延时 种子清选机研究现状与发展思考农机使用与维修(2022年12期)2022-12-16TGS智能梯流干选机在淮北矿业集团的应用选煤技术(2022年3期)2022-08-20一种带有通道功能新型风选机的应用科技信息·学术版(2021年8期)2021-01-10异色瓢虫在茄子上防治蚜虫的应用研究*上海蔬菜(2020年6期)2020-12-242种桃树蚜虫和天敌异色瓢虫对桃树品种趋性初探河北果树(2020年4期)2020-11-26基于级联步进延时的顺序等效采样方法及实现自动化仪表(2020年10期)2020-11-13日光灯断电关闭及自动延时开关设计电子制作(2019年14期)2019-08-20不同浓度吡虫啉对异色瓢虫捕食和繁殖行为的影响作物研究(2017年3期)2017-05-11血管萎缩性皮肤异色病1例中国中西医结合皮肤性病学杂志(2016年4期)2016-07-18Two-dimensional Eulerian-Lagrangian Modeling of Shocks on an Electronic Package Embedded in a Projectile with Ultra-high Acceleration船舶力学(2015年6期)2015-12-12- 上一篇:外贸毕业实习报告1五篇【精选推荐】

- 下一篇:2023年度酒店管理毕业实习报告8篇

猜你喜欢

- 2023-11-03 2023年度药学毕业实习总结14篇(完整文档)

- 2023-11-03 毕业工程实习总结系列3篇

- 2023-11-03 毕业大学生实习报告8篇

- 2023-11-03 有关设计类的实习报告6篇(范文推荐)

- 2023-11-03 2023年大专毕业个人实习总结14篇

- 2023-11-02 2023年优秀毕业实习总结11篇【通用文档】

- 2023-11-01 2023年度毕业实习汇报总结15篇(范例推荐)

- 2023-11-01 大学生毕业实训总结报告15篇

- 2023-10-31 大学生毕业实习工作总结13篇

- 2023-10-31 2023年品牌与ci设计5篇

- 搜索

-

- 党课讲稿:坚持政治建警全面从严治警 08-22

- “两新”组织党支部建设标准(试行) 11-11

- 3篇党员学习第三次中央新疆工作座谈会 09-28

- 《工程质量安全手册(试行)》(建质〔 08-26

- 基层党支部民主生活会批复 07-21

- 党员领导干部政治素质个人自评报告(范 06-10

- 党支部纪检委员职责 06-14

- 党支部组织生活会议内容 09-22

- 新任会长在协会换届选举大会上的讲话 03-25

- 工会会员(代表)大会选举办法 03-13

- 11-25国庆70周年庆典晚会 庆典晚会串词

- 11-25办公室礼仪的十大原则 浅谈办公室的电话礼仪

- 01-17用心灵轻轻地歌唱_心灵的歌唱

- 01-17也许你不是我一生的唯一|也许不是我

- 01-17爱了,请珍惜;不爱,趁早放手|爱就珍惜不爱就放手

- 01-17岁月带走的是记忆,但回忆会越来越清晰|有趣又有深意的句子

- 01-17曾经的美好只是曾经,我只想珍惜身边的人|我只想珍惜你

- 01-18从容不惊 [学会笑眼去看世界,不惊不乍,淡定从容]

- 02-03当代大学生学习态度调查报告

- 02-03常用护患英语会话

- 标签列表