首页 > 文秘写作 > 毕业设计 / 正文

基于PCIe的高精度低杂散信号源设计

2023-03-29 12:00:06 ℃段雄风,张 鹏

(1.中北大学仪器与电子学院,山西 太原 030051;

2.中北大学电子测试技术国家重点实验室,山西 太原 030051)

信号源能产生多种可调的激励信号,在电子电路、雷达遥测和军工航天等领域有着广泛的应用[1]。对压力信号采集测试仪器而言,一方面信号源为自测试设备模拟真实环境,产生测试波形信号,用于测试设备的正常功能指标;

另一方面高精度的信号源激励被测系统用于校准测试系统[2]。传统的信号源输出类型单一、精度低、误差较大、电路设计冗杂。目前,大多采用直接数字式频率合成器(direct digital synthesis,DDS)技术设计信号源系统。实现DDS信号生成的方案有2种。第一种是采用专用DDS芯片。这种方案控制简单、稳定性高,但是波形数据在内部存储器中固化,无法充分满足用户的各种需求。第二种是在现场可编程门阵列(field programmable gate array,FPGA)中根据需求实时产生任意可调波形。这种方案具有很强的灵活性[3]。

本文采用第二种方案,通过在FPGA中编程实现多功能高精度信号的发生(其中包括几种常用的基本信号与调制信号),并可根据用户需求通过上位机实时发送波形数据到FPGA,以产生任意波形的信号。在FPGA的可编程逻辑基础上,该方案灵活使用DDS与有限长单位冲激响应(finite impulse response,FIR)滤波器的相关知识产权(intellectual property,IP)核,针对信号杂散的产生原因进行分析处理,使输出信号满足高精度、低杂散的需求。另外,该方案通过高速串行计算机扩展总线(peripheral component interconnect express,PCIe)标准接口传输指令和波形数据,实现信号源的标准化和实时性,提供1种频率分辨率高、易于集成和小型化的多功能精密信号源产品。该产品方便集成在信号采集系统,用以输出稳定信号,并用于仪器自测试。

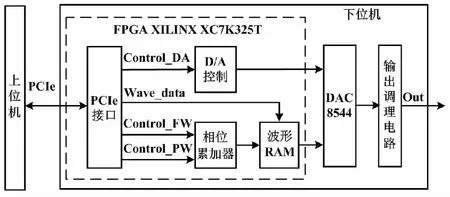

基于FPGA实现的信号源系统含上位机、主控制器FPGA、信号数模(digital to analog,D/A)转换和信号输出调理部分。上位机对要输出的波形数据进行量化,将量化后的数据和控制指令分别通过PCIe存入FPGA内的波形存储器和命令控制器,并采用控制频率控制字与相位控制字对查找表寻址提取对应数据,再由数字模拟转换器(digital to analog converter,DAC)和输出调理电路转为要求电压范围内的模拟信号[4]。PCIe的物理接口采用金手指插入主机卡槽。逻辑功能通过Xilinx公司提供的XDMA IP核实现,可配置AXI4-Lite 选项来访问用户逻辑侧寄存器。信号源系统整体如图1所示。

图1 信号源系统整体框图

当信号源工作时,设定的频率控制字FW决定了输出信号的频率,而相位控制字PW决定了信号的初始相位。信号的最小频率分辨率受相位累加器位数的影响,满足式(1):

(1)

当系统基准时钟不变、累加器的位数一定时,DDS输出信号的最小频率分辨率不会改变[5]。通常,为了获得较好的频率分辨率,会将相位N设置得比较大。

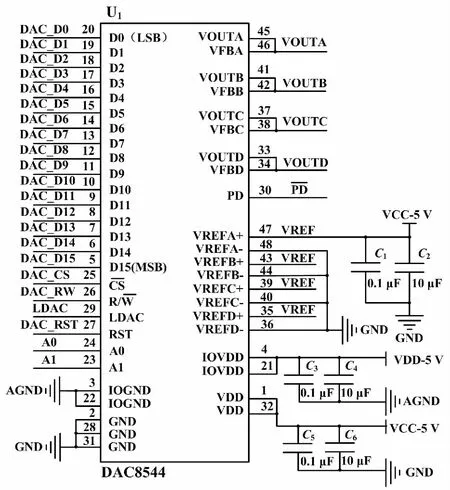

2.1 四通道D/A转换电路设计

在FPGA的信号发生逻辑设计中,波形随机存取存储器(ramdom access memory,RAM)存储的是连续数字量,需要经过D/A转换才能输出对应的模拟信号[6]。为满足设计需求,本文选择TI公司的低功耗4通道DAC8544芯片搭建D/A转换电路,以实现在初始化和复位时同步操作内部的转换器。该芯片采用并行输出接口,转换精度高达16位,内部含有精密输出放大器实现电压输出,并具有超低的串扰;

采用双电源供电,同时具有模拟和数字接地引脚,可以更好地控制返回电流,对输出误差影响较小。本文设计的D/A 转换电路如图2所示。

图2 D/A转换电路

DAC8544芯片通过外部参考电压来设置DAC的输出范围。其计算式为:

(2)

式中:UOUT为转换器输出电压,V;

D为转换器输入数字量。

根据所设计的UREF+为+5 V、UREF-接地为0 V,可得DAC输出范围为0~5 V。输入数据D经并行数据线DAC_D0~DAC_D15进入转换器,输出4路电压信号VOUTA~VOUTD。

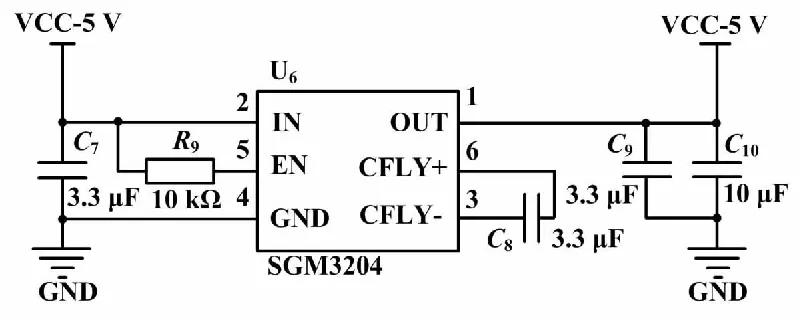

DAC8544芯片的双极性电源中,VCC-5 V模拟电源由PCIe插槽提供,同时经过SGM3204电压逆变器后,有效提供VCC-5 V负极性电源。电源转换电路如图3所示。

图3 电源转换电路

2.2 输出调理电路设计

为了获得双极性±5 V电压输出,要在输出的UOUT信号后接1个运算发大器OPA703,配置R1=R2=10 kΩ。此时,双极性输出Uk(k=1,2,3,4)可由式(3)得到。

(3)

经DAC转换后的模拟信号需要经过滤波处理,滤除输出信号中不必要的谐波分量[7]。本设计采用7阶椭圆滤波器,截止频率为10 MHz。该滤波器具有陡峭的衰减性,过度效果良好。双极性输出电路如图4所示。

图4 双极性输出电路

信号源系统的软件设计内容包括PCIe接口逻辑、信号发生逻辑、杂散处理与上位机软件。根据PCIe传输协议和DDS信号发生原理,在VIVADO软件中采用Verilog硬件描述语言进行设计。该系统采用Xilinx公司7系列的XC7K325T作为主芯片,具有丰富的逻辑存储资源[8]。在VIVADO开发平台中,可调用内部提供的XDMA IP核、RAM IP核与DDS Compiler IP核,从而降低系统的设计难度。

3.1 PCIe接口逻辑设计

PCIe接口用于实现上位机与FPGA之间的高速数据和命令的传输。本方案采用PCIe2.0 ×8接口,理论传输带宽可达到4 GB/s。Xilinx公司提供的XDMA IP核不仅对数据链路层和物理层的数据包进行了封装,而且处理了事务层传输线脉冲发生器(transmission line pulse,TLP)的组包解包。XDMA IP核的接口中,M_AXI和 M_AXI_ LITE接口都是数据传输接口。前者一般与先入先出(first input first ouput,FIFO)队列或双倍速率(double data rate,DDR)通信。后者一般用于配置信息,将数据存于双极随机存取存储器(bipolar access memory,BRAM)中。

对XDMA IP核进行配置时,选择×8通道、AXI接口数据位宽为128位、参考时钟为100 MHz。启动一次直接存储器访问(direct memory access,DMA)操作,总线开始传输多个非连续存储块数据,并在主机上对寄存器进行处理[9]。控制信息通过M_AXI_ LITE接口映射到BRAM用户逻辑地址。波形数据下发到DAC8544之前,通过M_AXI接口接到异步FIFO缓存,以保证信号发送的连续性。

3.2 信号发生逻辑设计

在本文设计中,基本信号类型的发生需按地址查询RAM中的波形数据表,调用Block Memory Generator IP核,申请1块BRAM地址空间。1个周期的波形数据以.coe文件存储在该空间中。同时,使用Xilinx公司的DDS IP核。DDS IP核集成了相位发生器和正余弦查找表的功能,可以设置成单独或组合使用,能产生连续的相位值寻址存储RAM。

调制波形的实现原理是在高频的载波信号中携带根据幅度或频率变化的低频信息[10]。调幅(ampltude modulation,AM)采用双DDS结构,分别产生调制信号Modulate_out与载波信号Carrier_out。调制信号经乘法器IP核与调制深度depth相乘,再经加法器IP核与直流分量A相加。调制深度在0~1之间,以0.1为间隔分为11个等级。加法器输出的信号与载波信号相乘就可以得到AM调制波形。该调制波形的幅度变化表示了调制信号内容,而其频率为载波信号频率。

AM信号实现逻辑如图5所示。

图5 AM信号实现逻辑框图

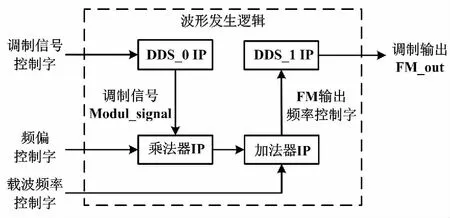

调频(frequency modulation,FM)调制波形的频率是随调制信号幅度变化而改变的,且幅值保持不变。设计时,设置FM调制波形的中心频率f0为5 MHz,最大频偏fd为4 MHz。该中心频率即为载波的频率。当输入调制信号幅度最大(即+215)时,将其与频偏设置值相乘,输出FM频率最大值为9 MHz。反之,当输入调制信号幅度最小(即-215)时,输出FM频率最小值为1 MHz。频偏后的频率控制字经加法器运算输出给DDS IP核,得到频率变化的FM调制波。FM信号实现逻辑如图6所示。

图6 FM信号实现逻辑框图

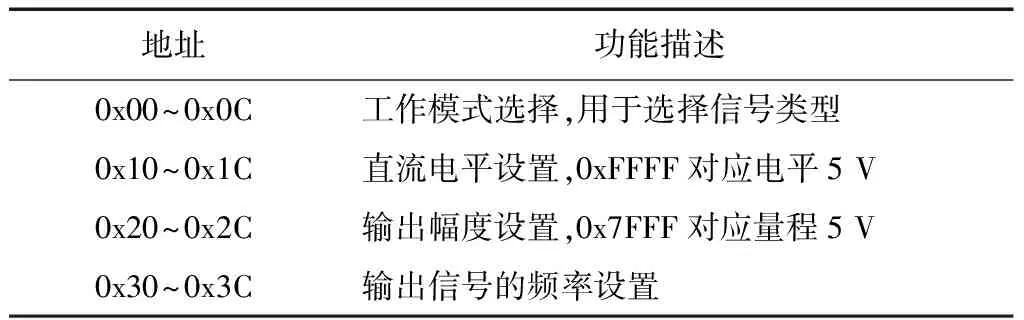

任意波形的实现均采用上位机下发自定义波形数据。上位机将自定义的波形数据存入主机寄存器,通过PCIe以DMA方式下发到用户逻辑侧寄存器,存入RAM后经过DAC输出。信号源的控制寄存器地址说明如表1所示。

表1 寄存器地址说明

3.3 杂散处理设计

经过分析,DDS信号源系统的杂散源自相位截断以及幅值量化的过程。为了获得较好的频率分辨率,本文设计系统时钟为100 MHz、DDS查找表相位宽度N为32位,再根据式(1)可得频率最小分辨率为0.023 Hz。但由于太高的相位宽度占用了很大的存储容量,会消耗芯片存储资源,本文使用相位截断,选择累加器的高16位进行波形数据表的寻址。由于相位截断造成可寻址的相位点变少,此时便引入了相位截断误差,使得输出波形引入杂散,并且分析相位误差序列可知其与输出的杂散均具有周期性[11]。另外,波形查找表中存储的是二进制数据,需要量化为波形的幅值。而在一般DDS方案中,并非波形存储器中的每个单独点都在结果输出波形中表示。相反,DDS输出波形的最佳近似值部分或完全跳过了波形中的小特征,严重时会导致失真。

针对相位截断引起的杂散具有周期性的特点,Xilinx提出1种相位抖动解决方案,即在DDS IP核中提供1种随机化信号,打破地址错误的规律性,提供约12 dB的无杂散动态范围[12]。设计者只需在配置IP核时,在系统参数的噪声整形选项中选中增加相位抖动,即可极大程度地提高输出信号的质量。针对幅值量化引起的杂散,本设计方案采用了插值滤波处理,使用Xilinx提供的FIR IP核,可对波形存储器输出的值实时内插,并实现低通滤波。FIR IP核中可导入带有滤波器设置参数的.coe文件。此文件可由MATLAB软件中的Filter Designer产生。在软件中的参数上选取采样频率为200 MHz、截止频率为10 MHz、滤波窗函数为Hamming、插值倍数为10倍。所设计的FIR归一化幅频特性曲线如图7所示。

图7 FIR 归一化幅频特性曲线

插值滤波过后的波形数据在不提高芯片分辨率的情况下,既节省了存储容量,又能通过DAC精确地反映信号的频率特性。

3.4 上位机软件设计

上位机软件基于LabVIEW平台设计,可实现人机交互功能。通过PCIe下发指令和波形数据,在选中并初始化信号源测试板卡后,对是否运行程序作出判断。若在运行状态下,则选择信号输出通道、信号的波形种类及幅值频率等参数。参数数据存放在规定地址的主板寄存器中。如4个通道的输出电压幅值寄存器地址范围为0x20、0x24、0x28、0x2C,对应地址处写入数值0~0x7FFF,即可输出幅值为0~5 V的电压。寄存器中的数据通过PCIe的DMA操作,直接与FPGA的存储单元进行传输,从而控制信号源的输出。上位机设计流程如图8所示。

图8 上位机设计流程图

在上位机界面中,用户使用鼠标点击布尔开关使能输出通道,通过键盘可写入幅值、频率等参数值。用户选择板卡及通道并设定参数后,可以在波形显示界面预览输出信号特征,以便使用。

4.1 PCIe数据传输

PCIe具有高带宽、高速数据传输能力的特点,通过上位机向FPGA发起DMA写操作,发送含目的地址、传输大小及数量信息的TLP配置寄存器。配置信息完成后,在上位机终端测试将一个大小为8 MB的bin文件传输到FPGA,同时再以二进制文件形式读取文件。经测试,8 388 608 B大小的数据写入时间为0.002 556 s,写数据速度为3 129.9 MB/s。此外,读取文件中的数据与发送数据一致,表明数据传输正确,具有很高的完整性。

4.2 四通道波形输出

将设计的信号源输出端连接到示波器后进行观察,可以在示波器上观察到波形输出。频率控制字FW设置为42 950时的正弦波,则测得波形输出频率为近似1 KHz,输出幅值为近似5 V,且波形无明显失真。

通过波形输出验证,本文设计的信号源输出频率范围为10 Hz~10 MHz,三角波与锯齿波频率最高为5 MHz,在范围内无明显失真情况。分别设置频率控制字为42 950、85 900、214 748、429 497,正弦波输出频率在1 kHz、2 kHz、5 kHz、10 kHz连续变化。正弦波变频输出曲线如图9所示。

图9 正弦波变频输出曲线

分析各频率点测量值与设置值的误差,虽然相对误差随频率变化波动,但都维持在0.01%~0.05%之间,精度高于传统信号源。正弦波输出频率误差分析如表2所示。

表2 正弦波输出频率误差分析

4.3 输出信号频谱分析

使用ROHDE&SCHWARZ示波器对信号的无杂散动态范围进行测试,使信号源输出5 MHz正弦信号。近端杂散测试范围在100 MHz以内,无杂散动态范围可达76.96 dB。输出信号杂散测试结果如表3所示。

表3 输出信号杂散测试结果

本文设计的高精度低杂散信号源基于FPGA与DAC8544芯片,利用Xilinx丰富的IP核资源,实现了4通道的任意信号输出。该信号源拥有多种波形输出类型及幅度频率可调的功能,通过PCIe发送波形数据,具备根据用户要求实时输出信号的能力。在信号发生逻辑中,创新使用FIR插值滤波技术,采用DDS IP核设计,利用相位抖动技术,输出信号频谱质量较好。输出信号频率误差比一般信号源误差更小、精度更高,同时电路体积与复杂程度更小。经试验验证,该信号源的功能丰富、使用方便,具有PCIe标准化接口,可制成板卡,集成于仪器仪表,用于压力测试系统,为测试系统提供模拟信号源。目前,该信号源模块已实现产品设计,并已应用于某冲击波压力测试仪。但本文设计还存在一些不足之处,后续研究还可以考虑提升输出信号的带宽,同时保证高频输出信号的频谱质量。

猜你喜欢 杂散信号源上位 VR技术在船舶通信系统天线信号源驻波检测中的应用舰船科学技术(2022年10期)2022-06-17关于杂散辐射产生原因及解决方法的研究*通信技术(2020年6期)2020-07-19无线电发射设备杂散发射的测试方法探讨现代经济信息(2020年34期)2020-06-08基于FreeRTOS操作系统的地铁杂散电流监测系统铁道通信信号(2020年9期)2020-02-06特斯拉 风云之老阿姨上位车迷(2018年12期)2018-07-26一切以“大” 方向发展 20周年影音系统变迁史(信号源篇)家庭影院技术(2017年8期)2017-10-13聚焦4K视频播放展望未来信号源发展家庭影院技术(2017年9期)2017-09-26“三扶”齐上位 决战必打赢中国老区建设(2016年3期)2017-01-15基于ZigBee和VC上位机的教室智能监测管理系统山东工业技术(2016年15期)2016-12-01发射机信号源的自动处理和控制系统西部广播电视(2015年5期)2016-01-16猜你喜欢

- 2023-11-03 2023年度药学毕业实习总结14篇(完整文档)

- 2023-11-03 毕业工程实习总结系列3篇

- 2023-11-03 毕业大学生实习报告8篇

- 2023-11-03 有关设计类的实习报告6篇(范文推荐)

- 2023-11-03 2023年大专毕业个人实习总结14篇

- 2023-11-02 2023年优秀毕业实习总结11篇【通用文档】

- 2023-11-01 2023年度毕业实习汇报总结15篇(范例推荐)

- 2023-11-01 大学生毕业实训总结报告15篇

- 2023-10-31 大学生毕业实习工作总结13篇

- 2023-10-31 2023年品牌与ci设计5篇

- 搜索

-

- 党课讲稿:坚持政治建警全面从严治警 08-22

- “两新”组织党支部建设标准(试行) 11-11

- 3篇党员学习第三次中央新疆工作座谈会 09-28

- 《工程质量安全手册(试行)》(建质〔 08-26

- 基层党支部民主生活会批复 07-21

- 党员领导干部政治素质个人自评报告(范 06-10

- 党支部纪检委员职责 06-14

- 党支部组织生活会议内容 09-22

- 新任会长在协会换届选举大会上的讲话 03-25

- 工会会员(代表)大会选举办法 03-13

- 11-25国庆70周年庆典晚会 庆典晚会串词

- 11-25办公室礼仪的十大原则 浅谈办公室的电话礼仪

- 01-17用心灵轻轻地歌唱_心灵的歌唱

- 01-17也许你不是我一生的唯一|也许不是我

- 01-17爱了,请珍惜;不爱,趁早放手|爱就珍惜不爱就放手

- 01-17岁月带走的是记忆,但回忆会越来越清晰|有趣又有深意的句子

- 01-17曾经的美好只是曾经,我只想珍惜身边的人|我只想珍惜你

- 01-18从容不惊 [学会笑眼去看世界,不惊不乍,淡定从容]

- 02-03当代大学生学习态度调查报告

- 02-03常用护患英语会话

- 标签列表